Rocktech Displays Limited

| Module P/N  | I: <u>RK014CE06A</u>                                                     |

|-------------|--------------------------------------------------------------------------|

| Version:    | 2.0                                                                      |

| Description | : 1.44 inch TFT 128*128 Pixels with<br>LED backlight,140 nits brightness |

| TEL:        | 0086-755-26065260                                                        |

| Fax:        | 0086-755-26065261                                                        |

| E-mail:     | Sales@rocktech.com.hk                                                    |

| Web:        | www.rocktech.com.hk                                                      |

# **Revision History**

| Date       | Rev. | Page   | Description    |

|------------|------|--------|----------------|

| 05/03/2013 | 1.0  | All    | First issue    |

| 01/09/2015 | 2.0  | Page15 | Change the BKL |

|            |      |        |                |

# CONTENTS

- GENERAL FEATURES

- ABSOLUTE MAXIMUM RATINGS

- ELECTRICAL SPECIFICATIONS

- OPTICAL SPECIFICATIONS

- BLOCK DIAGRAM

- PIN DESCRIPTION

- TIMING CHARACTERISTICS

- OUTLINE DIMENSION

- RELIABILITY AND INSPECTION STANDARD

- PRECAUTIONS

# 1. General Features

| ltem                   | Spec                        | Remark |

|------------------------|-----------------------------|--------|

| Display Mode           | Normally White transmissive |        |

| Viewing Direction      | 12 O'CLOCK                  |        |

| Input Signals          | 8 bits parallel or SPI      |        |

| Outline Dimensions(mm) | 32.36(W) x38.00(H) x2.60(D) |        |

| Active Area(mm)        | 25.50mm(W)×26.50mm(H)       |        |

| Number of Pixels       | 128(RGB)×128                |        |

| Dot Pitch(mm)          | 0.207mm(W) ×0.207mm(H)      |        |

| Pixel Arrangement      | RGB Vertical stripes        |        |

| Drive IC               | ST7735S                     |        |

# 2. Absolute Maximum Ratings

The following are maximum values which, if exceeded may cause operation or damage to the unit.

| ITEM                              | Sym.            | Min. | Тур. | Max. | Unit | Remark        |

|-----------------------------------|-----------------|------|------|------|------|---------------|

| Power for Circuit Driving         | VDD             | -0.3 | -    | 4.6  | V    |               |

| Logic Signal Input/output Voltage | Vddi            | -0.3 | -    | 4.6  | V    |               |

| Storage Humidity                  | H <sub>ST</sub> | 10   | -    |      | %RH  |               |

| Storage Temperature               | T <sub>ST</sub> | -30  | -    | 80   | °C   | At            |

| Operating Ambient Humidity        | H <sub>OP</sub> | 10   | -    |      | %RH  | <b>25±5</b> ℃ |

| Operating Ambient temperature     | T <sub>OP</sub> | -20  | -    | 70   | °C   |               |

## 3. Electrical Specification

#### 3.1 Driving TFT LCD Panel

| ltem         |                 | Sym. | Min    | Тур. | Max    | Unit | Note |

|--------------|-----------------|------|--------|------|--------|------|------|

| Power for (  | Circuit Driving | VDD  | 2.3    | 2.8  | 3.3    | V    |      |

| Logic Input  | Low Voltage     | VIL  | 0      | -    | 0.3VDD | V    |      |

| Voltage      | High Voltage    | Vін  | 0.7VDD | -    | VDD    | V    |      |

| Logic Output | Low Voltage     | Vol  | 0      | -    | 0.2VDD | V    |      |

| Voltage      | High Voltage    | Vон  | 0.8VDD | -    | -      | V    |      |

# 3.2 Driving Backlight

| Item                        | Sym. | Min | Тур.   | Мах | Unit | Note   |

|-----------------------------|------|-----|--------|-----|------|--------|

| Backlight driving voltage   | Vf   | -   | 3.2    | -   | V    |        |

| Backlight driving current   | lf   | 15  | 20     | 25  | mA   |        |

| Backlight Power Consumption | WBL  | -   | 64     | -   | mW   |        |

| Lift Time                   | -    | -   | 50,000 | -   |      | Note 3 |

Note 1: (Unless specified, the ambient temperature  $Ta=25^{\circ}C$ )

Note 2: The recommended operating conditions refer to a range in which operation of this product is guaranteed. Should this range is exceeded, the operation cannot be guaranteed even if the values may be without the absolute maximum ratings.

Note 3: If LED is driven by high current, high ambient temperature & humidity condition. The life time of LED will be reduced. Operating life means brightness goes down to 50% initial brightness. Typical operating life time is estimated data.

#### **4.Optical Specifications**

Optical characteristics are determined after the unit has been 'ON' and stable for approximately 30 minutes in a dark environment at 25 °C. The values specified are at an approximate distance 500mm from the LCD surface at a viewing angle of  $\Phi$  and  $\theta$  equal to  $0^{\circ}$ .

| lto                | Creme        |       | Values |       |                   | Nata  |  |

|--------------------|--------------|-------|--------|-------|-------------------|-------|--|

| ltem               | Sym.         | Min.  | Тур.   | Max.  | Unit              | Note  |  |

| 1)Contrast Ratio   | C/R          | -     | 300    | -     |                   | FIG.1 |  |

| 2)Module Luminance | L            | 90    | 140    | -     | cd/m <sup>2</sup> | FIG.1 |  |

| 3)Response time    | Tr+Tf        | -     | 20     | -     | ms                | FIG.2 |  |

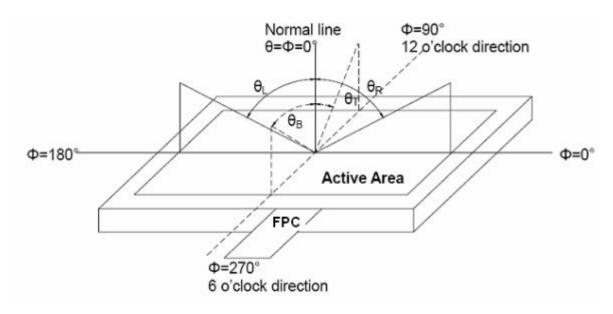

|                    | θτ           | -     | 60     | -     |                   |       |  |

|                    | $\theta_{B}$ | -     | 50     | -     | Deeree            |       |  |

| 4)Viewing Angle    | θ∟           | -     | 60     | -     | Degree            | FIG.3 |  |

|                    | $\theta_{R}$ | -     | 60     | -     |                   |       |  |

|                    | Wx           | 0.265 | 0.305  | 0.345 |                   |       |  |

|                    | Wy           | 0.308 | 0.348  | 0.388 |                   |       |  |

|                    | Rx           | -     | -      | -     |                   |       |  |

| 5)Chromaticity     | Ry           | -     | -      | -     |                   |       |  |

|                    | Gx           | -     | -      | -     |                   |       |  |

|                    | Gy           | -     | -      | -     |                   |       |  |

|                    | Bx           | -     | -      | -     |                   |       |  |

|                    | Ву           | -     | -      | -     |                   |       |  |

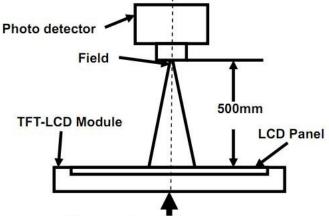

#### Measurement System

#### Notes:

#### Surface Luminance with all black pixels

- 2. Surface luminance is the center point across the LCD surface 500mm from the surface with all pixels displaying white. For more information see FIG 1.

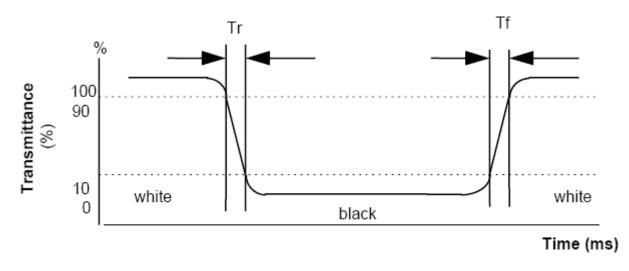

- 3. Response time is the time required for the display to transition from white to black (Rising Time, Tr) and from black to white (Falling Time, Tf). For additional information see FIG 2.

- 4. Viewing angle is the angle at which the contrast ratio is greater than 10. The angles are determined for the horizontal or x axis and the vertical or y axis with respect to the z axis which is normal to the LCD surface. For more information see FIG 3.

#### FIG. 1 Optical Characteristic Measurement Equipment and Method

| Item           | Photo detector | Field |  |

|----------------|----------------|-------|--|

| Contrast Ratio |                |       |  |

| Luminance      |                | 40    |  |

| Chromaticity   | SR-3A          | 1°    |  |

| Lum Uniformity |                |       |  |

| Response Time  | BM-7A          | 2°    |  |

The center of the screen

#### FIG. 2 The definition of Response Time

The response time is defined as the following figure and shall be measured by switching the input signal for "black" and "white".

Response Time = Rising Time(Tr) + Falling Time(Tf)

- Rising Time(Tr) : Full White 90%  $\rightarrow$  Full White 10% Transmittance.

- Falling Time(Tf) : Full White 10%  $\rightarrow$  Full White 90% Transmittance.

#### FIG. 3 The definition of Viewing Angle

Use Fig. 1(Test Procedure) under Measurement System to measure the contrast from the measuring direction specified by the conditions as the following figure.

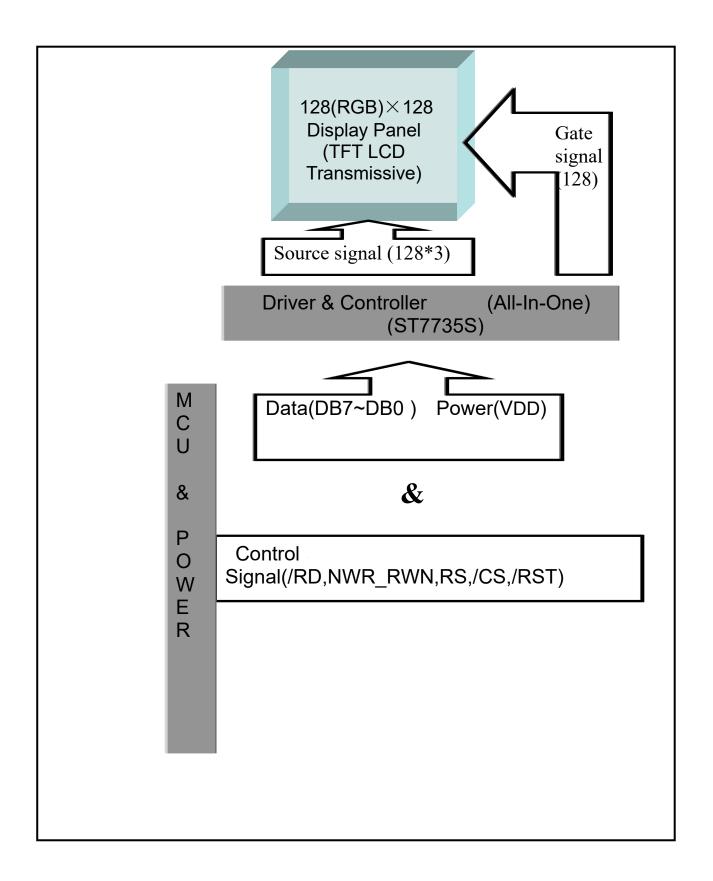

## 5. Block Diagram Block Diagram

# 6. Pin Description

| Pin No. | Symbol     | I/O    | Function                                                                                                                                                  |

|---------|------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | NC         | -      | No Connect.                                                                                                                                               |

| 2       | LED+       | I      | Anode for LED backlighting                                                                                                                                |

| 3       | LED-       | I      | Cathode for LED backlighting                                                                                                                              |

| 4~7     | NC         | -      | No Connect.                                                                                                                                               |

| 8       | VDD        | Ρ      | Power Supply for Analog Circuit(2.8V typ.)                                                                                                                |

| 9       | GND        | PG     | Power Ground.                                                                                                                                             |

| 10      | VDDI       | Ρ      | Power Supply for Logic Circuit(1.8V/2.8V typ.)                                                                                                            |

| 11      | NC         | -      | No Connect.                                                                                                                                               |

| 12      | /CS        | Ĩ      | Chip select signal                                                                                                                                        |

| 13      | IM2        | I      | MCU Parallel interface bus and Serial interface select<br>- IM2='1';Parallel Interface<br>- IM2='0';Serial Interface                                      |

| 14      | SPI4W      | 1      | SPI4W=0: 3-wire serial interface (default)<br>Use pins are: /CS,SDA,DNC_SCL,<br>SPI4W=1: 4-wire serial interface<br>Use pins are:/CS,SDA,DNC_SCL,NWR_RNW. |

| 15      | /RST       | I      | Chip reset pin                                                                                                                                            |

| 16      | /RD        | 1      | Read control pin; In 8080-parallel interface, if not used, please connect this pin to VDDI.                                                               |

| 17      | VDDI       | Р      | Power Supply for Logic Circuit(1.8V/2.8V typ.)                                                                                                            |

| 18      | DB7        | I/O    |                                                                                                                                                           |

| 19      | DB6        | I/O    |                                                                                                                                                           |

| 20      | DB5        | I/O    |                                                                                                                                                           |

| 21      | DB4        | I/O    | 8 bit parallel data bus interface.<br>While, D0 is also the serial input/ output signal in SPI interface                                                  |

| 22      | DB3        | I/O    | mode, D0 sever as a SDA pin . In serial interface, D[7:1] are not used and should be connected to ground.                                                 |

| 23      | DB2        | I/O    | not used and should be connected to ground.                                                                                                               |

| 24      | DB1        | I/O    |                                                                                                                                                           |

| 25      | DB0/SDA    | I/O    |                                                                                                                                                           |

| 26      | NWR_RNW    | I      | Write control pin; While in Serial Interface<br>Serve as D/CX: for 4-wire SPI                                                                             |

| 27      | RS/DNC_SCL | Ĩ      | Data/command selection pin; While in Serial Interface serve as SCL.                                                                                       |

| 28      | ID         | -      | LCM Identity. If not used, let it open.                                                                                                                   |

| 29      | NC         | )<br>J | No Connect.                                                                                                                                               |

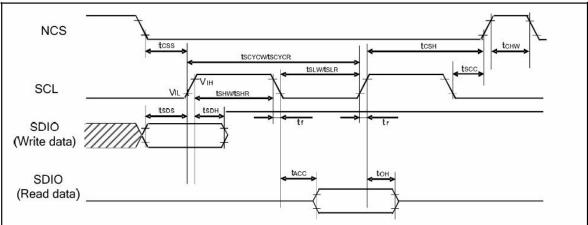

#### 7. Interface Timing Chart

7.1 Serial interface characteristics

Figure 1 Serial Interface Timing Characteristics

| Parameter                   | Symbol | Conditions                                       |      | Unit  |           |       |

|-----------------------------|--------|--------------------------------------------------|------|-------|-----------|-------|

| Farameter                   | Symbol | Conditions                                       | Min. | Тур.  | Typ. Max. |       |

| Serial clock cycle (Write)  | tSCYCW |                                                  | 33   |       | •         |       |

| SCL "H" pulse width (Write) | tSHW   | SCL                                              | 10   | -     |           | ns    |

| SCL "L" pulse width (Write) | tSLW   |                                                  | 10   | 10-10 | 8.00      | 0.338 |

| Data setup time (Write)     | tSDS   | 2010                                             | 10   |       | •         |       |

| Data hold time (Write)      | tSDH   | I SDIO                                           |      | . G   | •         | ns    |

| Serial clock cycle (Read)   | tSCYCR | 1-11-0-18                                        | 150  | 1.20  | <u></u>   |       |

| SCL "H" pulse width (Read)  | tSHR   | SCL                                              | 60   | -     |           | ns    |

| SCL "L" pulse width (Read)  | tSLR   |                                                  | 60   | -     |           |       |

| Access Time                 | tACC   | SDI for maximum<br>CL=30pF<br>For minimum CL=8pF | 10   | 1.1   | 50        | ns    |

| Output disable time         | tOH    | SDO For maximum                                  |      |       | 50        | ns    |

| SCL to Chip select          | tSCC   | SCL, NCS                                         | 20   |       | 1.00      | ns    |

| NCS "H" pulse width         | tCHW   | NCS                                              | 40   | -     | -         | ns    |

| Chip select setup time      | tCSS   | NCS                                              | 15   | -     |           |       |

| Chip select hold time       | tCSH   | NCO                                              | 15   | -     |           | ns    |

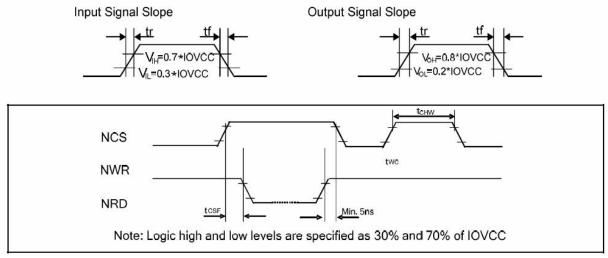

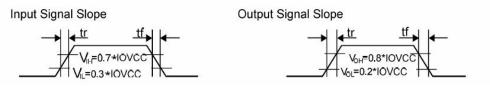

Note: The input signal rise time and fall time (tr, tf) is specified at 15 ns or less.

Logic high and low levels are specified as 30% and 70% of IOVCC for Input signals.

Figure 2 Chip Selection Timing

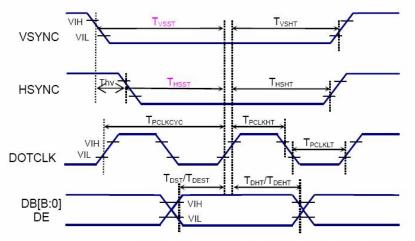

#### 7.2 RGB interface characteristics

(VSSA=0V, IOVCC=1.65V to 3.3V, VCI=2.3V to 3.3V, Ta = -30 to 70° C)

| ltem                                            | Symbol Condition   |                 |      | Spec.      |                |        |

|-------------------------------------------------|--------------------|-----------------|------|------------|----------------|--------|

|                                                 | Symbol             | Condition       | Min. | Тур.       | Max.           | Unit   |

| Pixel low pulse width                           | T <sub>CLKLT</sub> | 3 <del></del>   | 15   |            |                | ns     |

| Pixel high pulse width                          | T <sub>CLKHT</sub> | -               | 15   |            | -              | ns     |

| Vertical Sync. set-up time                      | T <sub>VSST</sub>  | ( <del>1</del>  | 15   | -          | -              | ns     |

| Vertical Sync. hold time                        | T <sub>VSSHT</sub> | . <del></del>   | 15   |            |                | ns     |

| Horizontal Sync. set-up time                    | T <sub>HSST</sub>  | -               | 15   | -          | -              | ns     |

| Horizontal Sync. hold time                      | T <sub>VSSHT</sub> | -               | 15   | <u>-</u>   | 1 <u>-</u> 2)  | ns     |

| Data Enable set-up time                         | T <sub>DEST</sub>  | 8 <b>.</b>      | 15   |            | 1.0            | ns     |

| Data Enable hold time                           | T <sub>DEHT</sub>  | -               | 15   | . <b>.</b> |                | ns     |

| Data set-up time                                | T <sub>DST</sub>   | 8 <b>11</b> 9   | 15   | <b>1</b> 1 | 1211           | ns     |

| Data hold time                                  | T <sub>DHT</sub>   | 8 <del></del> ) | 15   |            | 1 <del>.</del> | ns     |

| Phase difference of sync signal<br>falling edge |                    |                 | 0    | -          | 240            | Dotclk |

Note: The input signal rise time and fall time (tr, tf) is specified at 15 ns or less.

Figure 3 RGB interface characteristics

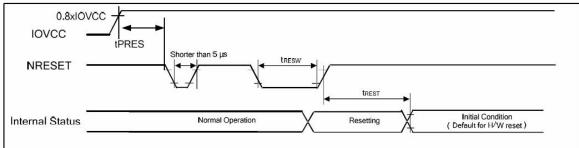

#### 7.3 Reset Input Timing

| Figure  | 4 Reset  | Input | Timing    |

|---------|----------|-------|-----------|

| 1 15010 | 1 100000 | mpat  | 1 1111115 |

| Symbol | Parameter                                    | Related<br>Pins   | Spec. |      |            | Note                                      | Unit |

|--------|----------------------------------------------|-------------------|-------|------|------------|-------------------------------------------|------|

|        |                                              |                   | Min.  | Тур. | Max.       | Note                                      | Unit |

| tRESW  | Reset low pulse width <sup>(1)</sup>         | NRESET            | 10    |      | 17         | <del></del>                               | μs   |

| tREST  | Reset complete time <sup>(2)</sup>           | -                 | 5     | -    |            | When reset applied<br>during STB OUT mode | ms   |

|        |                                              | -                 | 120   | -    |            | When reset applied<br>during STB mode     | ms   |

| tPRES  | Reset goes high level<br>after Power on time | NRESET &<br>IOVCC | 1     | -    | <b>H</b> ) | Reset goes high level<br>after Power on   | ms   |

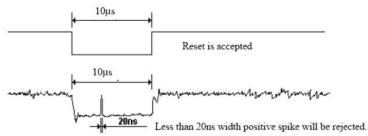

Note: (1) Spike due to an electrostatic discharge on NRESET line does not cause irregular system reset according to the table below.

| NRESET Pulse           | Action         |

|------------------------|----------------|

| Shorter than 5 µs      | Reset Rejected |

| Longer than 10 µs      | Reset          |

| Between 5 µs and 10 µs | Reset Start    |

- (2) During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in STB Out –mode. The display remains the blank state in STB –mode) and then return to Default condition for H/W reset.

- (3) During Reset Complete Time, VMF value in OTP will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time (tREST) within 5ms after a rising edge of NRESET.

- (4) Spike Rejection also applies during a valid reset pulse as shown below:

(5) It is necessary to wait 5msec after releasing !RES before sending commands. Also STB Out

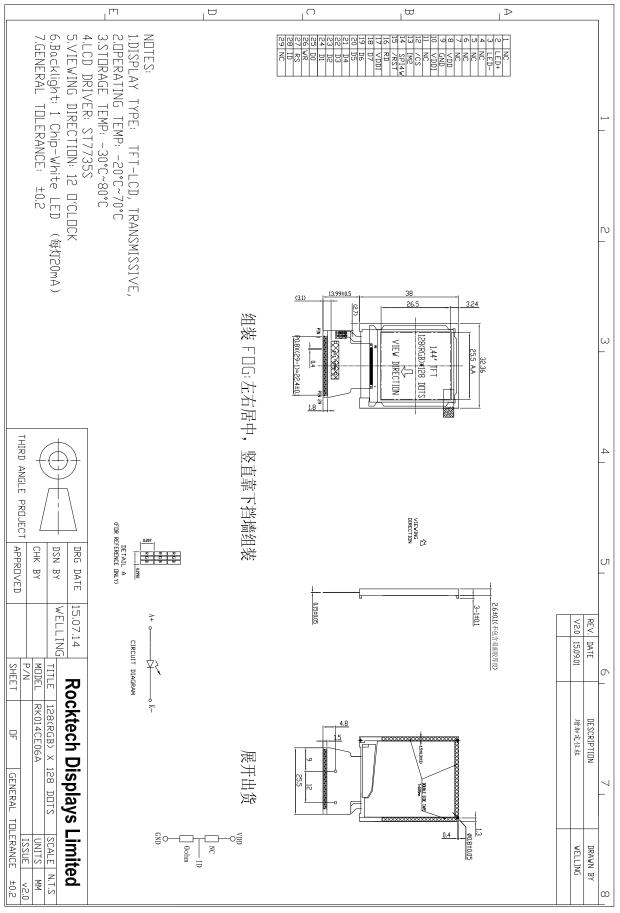

# 8.Outline Dimension

# 9. Reliability and Inspection Standard

| No. | Test Item                             |            | Test Conditions                                                                                                            | Remark |  |

|-----|---------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------|--------|--|

| 1   | High Temperature                      | Storage    | <b>80</b> ℃, 120Hr                                                                                                         | Note   |  |

|     |                                       | Operation  | <b>70°</b> ℃, <b>120H</b> r                                                                                                | Note   |  |

| 2   | Low Temperature                       | Storage    | <b>-30</b> ℃, 120Hr                                                                                                        | Note   |  |

|     |                                       | Operation  | <b>-20</b> ℃, 120Hr                                                                                                        |        |  |

| 3   | High Temperature and High<br>Humidity |            | 40℃, 90%RH, 120Hr                                                                                                          | Note   |  |

| 4   | Thermal Cycling Test(No operation)    |            | -20℃ for 30min, 70℃ for 30 min.<br>100 cycles. Then test at room<br>temperature after 1 hour                               | Note   |  |

| 5   | Vibration Test(No o                   | operation) | Frequency :10~55 HZ; Stroke :1.5<br>mm;Sweep:10HZ~55HZ~10HZ;<br>2hours for each direction of X, Y, Z(6<br>hours for total) |        |  |

| 6   | Package Drop Test                     |            | Height:60 cm,1 corner, 3 edges,<br>6 surfaces                                                                              |        |  |

| 7   | Electro Static Discharge              |            | $\pm$ 2KV,Human Body Mode, 100pF/1500Ω                                                                                     |        |  |

Note:

1) Sample quantity for each test item is 5~10pcs.

2) Note 4: Before cosmetic and function test, the product must have enough recovery time, at least 2 hours at room temperature.

# **10.PRECAUTIONS FOR USING LCD MODULES**

#### **Handing Precautions**

- (1) The display panel is made of glass and polarizer. As glass is fragile, it tends to become or chipped during handling especially on the edges. Please avoid dropping or jarring. Do not subject it to a mechanical shock by dropping it or impact.

- (2) If the display panel is damaged and the liquid crystal substance leaks out, be sure not to get any in your mouth. If the substance contacts your skin or clothes, wash it off using soap and water.

- (3) Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary. Do not touch the display with bare hands. This will stain the display area and degraded insulation between terminals (some cosmetics are determined to the polarizer).

- (4) The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully. Do not touch, push or rub the exposed polarizers with anything harder than an HB pencil lead (glass, tweezers, etc.). Do not put or attach anything on the display area to avoid leaving marks on. Condensation on the surface and contact with terminals due to cold will damage, stain or dirty the polarizer. After products are tested at low temperature they must be warmed up in a container before coming is contacting with room temperature air.

- (5) If the display surface becomes contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If it is heavily contaminated, moisten cloth with one of the following solvents

- Isopropyl alcohol

- Ethyl alcohol

- Do not scrub hard to avoid damaging the display surface.

- (6) Solvents other than those above-mentioned may damage the polarizer. Especially, do not use the following.

- Water

- Ketone

- Aromatic solvents

Wipe off saliva or water drops immediately, contact with water over a long period of time may cause deformation or color fading. Avoid contacting oil and fats.

- (7) Exercise care to minimize corrosion of the electrode. Corrosion of the electrodes is accelerated by water droplets, moisture condensation or a current flow in a high-humidity environment.

- (8) Install the LCD Module by using the mounting holes. When mounting the LCD module make sure it is free of twisting, warping and distortion. In particular, do not forcibly pull or bend the I/O cable or the backlight cable.

- (9) Do not attempt to disassemble or process the LCD module.

- (10) NC terminal should be open. Do not connect anything.

- (11) If the logic circuit power is off, do not apply the input signals.

- (12) Since LCM has been assembled and adjusted with a high degree of precision, avoid applying excessive shocks to the module or making any alterations or modifications to it.

- Do not alter, modify or change the shape of the tab on the metal frame.

- Do not make extra holes on the printed circuit board, modify its shape or change the positions of components to be attached.

- Do not damage or modify the pattern writing on the printed circuit board.

- Absolutely do not modify the zebra rubber strip (conductive rubber) or heat seal

connector.

- Except for soldering the interface, do not make any alterations or modifications with a soldering iron.

- Do not drop, bend or twist LCM.

#### **Storage Precautions**

When storing the LCD modules, the following precaution is necessary.

- (1) Store them in a sealed polyethylene bag. If properly sealed, there is no need for the dessicant.

- (2) Store them in a dark place. Do not expose to sunlight or fluorescent light, keep the temperature between 0°C and 35°C.

- (3) The polarizer surface should not come in contact with any other objects. (We advise you to store them in the container in which they were shipped).

#### Others

Liquid crystals solidify under low temperature (below the storage temperature range) leading to defective orientation or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subject to a low temperature. If the LCD modules have been operating for a long time showing the same display patterns, the display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. A normal operating status can be regained by suspending use for some time. It should be noted that this phenomenon does not adversely affect performance reliability.

To minimize the performance degradation of the LCD modules resulting from destruction caused by static electricity etc., exercise care to avoid holding the following sections when handling the modules.

- Exposed area of the printed circuit board.

-Terminal electrode sections.